FPGA Design Services

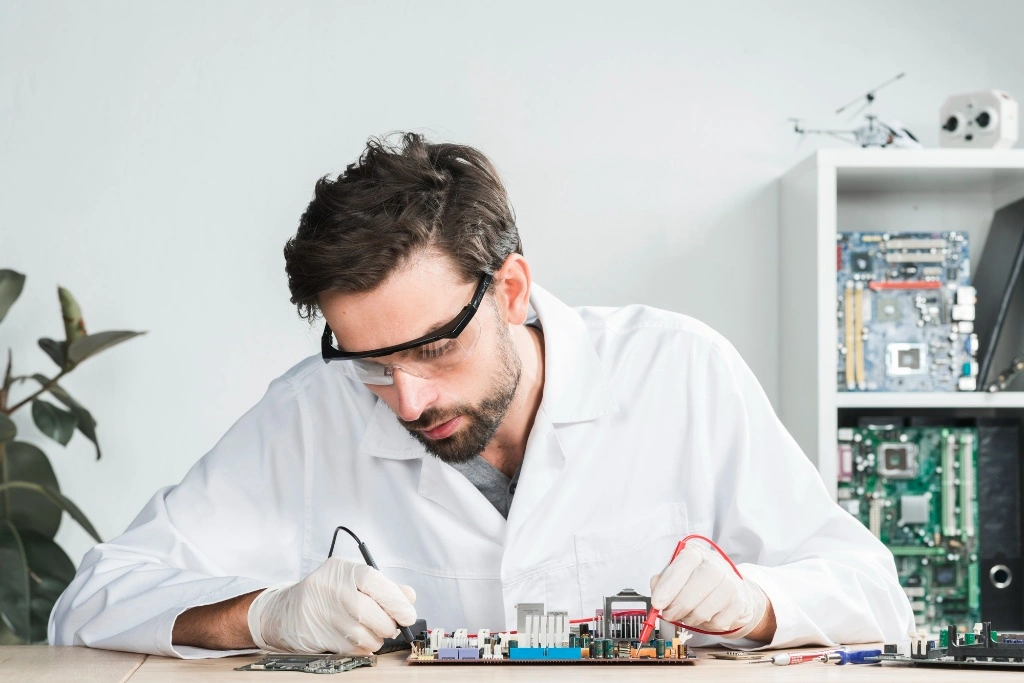

Future-proof your telecommunication and aerospace layouts with our end-to-end FPGA design services. With the help of custom IP and peripheral design, we create an FPGA RTL model that maximizes performance-per-watt. Also, the HLS methodologies and UVM verification ensure first-pass success for your FPGA-based systems. All in all, Netiqate is your best bet for next-generation telecommunication, digital infrastructure, and aerospace applications.

Get Your Hands On Our High-Level FPGA Synthesis Workflows

There’s a reason why we specialize in FPGA design of MPSoC and RFSoC platforms. Our team is well-versed in integrating the custom programmable logic design with ARM-based processing. The best thing about these services is the FPGA RTL design flow. It helps businesses minimize the gap between C/C++ algorithms and RTL manufacturing.

- Unmatched AI Acceleration

- HLS-Optimized IP Cores

- Bare-Metal/RTOS Firmware Support

- Multi-Gigabit SterDes Optimization

Why Choosing Us Gets You A “Gold Standard” FPGA Excellence

Unlike other FPGA system architecture companies, we do not stop at traditional perks. On the contrary, we use specialized AI systems, modern HDLs (Verilog, VHDL) equipment, DVI video inputs and exceptional post-synthesis simulation. Check out four specific reasons why we are the perfect fit for your business:

UVM-Backed Verification

Building robust and reusable testbenches using Universal Verification Methodology (UVM) is not rocket science for Netiqate specialists. The team not only performs the task efficiently but also provides full code coverage and functional verification.

HLS Acceleration

HLS is your best ally to eliminate the impacts caused by the gaps between digital algorithms and RTL. Also, it enabled businesses to rapidly explore Edge AI and DSP kernels without compromising on performance-per-watt efficiency.

Heterogeneous System-on-Chip Integration

Our firm is a leading name in RFSoC and MPSoC architectures. Effectively partitioning tasks between ARM processors and algorithms is one of the primary areas of expertise of the company. Besides, we use AXI-interconnects, which ensure ultra-low latency data movement in mission-critical systems.

CDC Specialization and Deterministic Timing

If you need a firm that guarantees timing closure on high-frequency designs by resolving Clock Domain Crossings (CDC), Netiqate is the name for you! Using Static Time Analysis (STA), we eliminate metastable states. Consequently, you get designs that are 100% hardware synchronized.

Digital Supremacy That Actually Works!

Functional and timing simulation is not dependent on theoretical tactics alone. Exceptional software programs are necessary for the design’s first-pass success. So, our team uses Ansys HFSS, CST Studio Suite, Keysight ADS, and Cadence design systems in correlation to get the best results.

Next-Gen FPGA-Based Sub-Services Of Netiqate

Abstract algorithms and physical hardware deliver high performance when used together. Our team uses the same hardware logic design in our sub-services and supplies precisely engineered FPGA layouts to businesses.

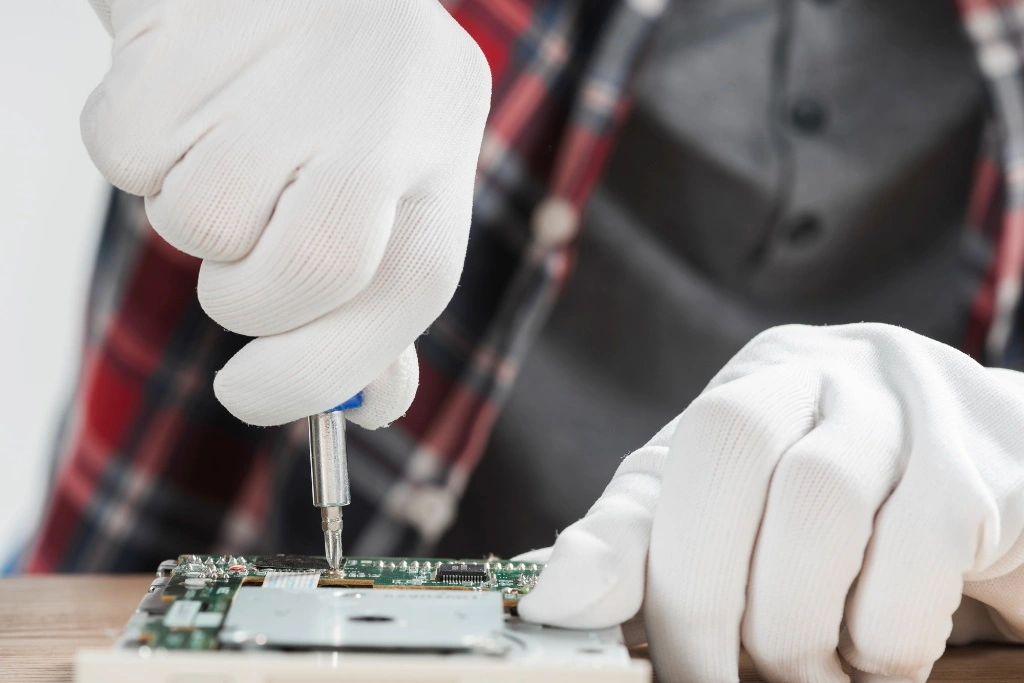

FPGA Designs For Embedded Systems

The primary factor that helps our embedded system FPGA designs stand out is the integration of ARM-based MPSoC and soft-core processors for designing.

FPGA RTL Design

To guarantee supremacy of design for test (DFT) in FPGA systems, we use VHDL/SystemVerilog RTL. Also, the team uses UVM testbenches to ensure absolute data integrity across SerDes lanes.

FPGA Schematic Design

Our FPGA schematic designs feature optimized PDN decoupling and impedance matching. If your project is similar to BGA architecture, our multi-rail power sequencing will serve you ideally.

Custom FPGA Design Services For Terabit Data Paths

I/O bottlenecks are no longer a problem with our custom electronics design solutions by your side. Our team engineers PCIe GEN 6.0 interfaces and multi-channel DMA engines to manage massive data flows. Contact the specialists and check which UVM-validated protocols we follow!

High-Efficiency IP Core Integration For FPGA Designing

Maximum resource efficiency is ensured at Netiqate through optimization of third-party and custom IP cores. The team uses AXI4-stream interfacing and bit-accurate modeling. That’s how we reduce the footprint on AMD Versal and Intel Agilex designs.

Based on the 6G RAN accelerators, we optimize FPGA systems to withstand rigorous conditions without jeopardizing signal integrity or digital processing power. Simultaneously, the hardware description languages of Verilog minimize algorithmic confusions once and for all!

The FPGA Design Company With AES-256 Bitstream Encryption

Get the safest FPGA designing services in just a click!

Code-Compliance For Mission-Critical Reliability

As one of the top FPGA designing companies, we believe in adhering to all necessary codes and standards while designing layouts. So, the team follows DO-254 and MIL-STD-883 protocols. Moreover, our high-density interconnect layouts comply with IPC-2221B and IPC-7351B.

Experts at Netiqate also keep ISO 26262 and NIST SP 800-193 in mind. These help design FPGA systems that are compliant on the basis of automotive functional safety and hardware platform resiliency. Also, the implementation of MISRA C++ rules to HLS workflows creates tamper-proof designs.

Innovative FPGA Solutions Across Multiple Industrial Fronts

When it comes to circuit and layout designing, we are not confined to a single industrial application. Our experts provide FPGA design to every industry where deterministic timing and ultra-low latency are non-negotiable. Here are the two primary industries we serve:

Telecommunication:

In the telecommunication industry, our custom FPGA design services are all about optimization of 6G RAN and Open-RAN (O-RAN) accelerators. Also, we use beamforming IP and LDPC/Turbo decoders to handle multi-terabit throughput.

Read More >

Aerospace Industry

We design RAD-hardened flight logic and SEU-resilient FPGA designs for satellite payloads. The team also implements Triple Modular Redundancy (TMR) and SpaceWire/RapidIO interfaces. It helps in mission-critical orbital data processing.

Read More >

Client Success Stories

Lead FPGA Designer At El-Labs

Hardware operator at DT Engineering

Senior System Engineer At Bard Technologies

Consult with Our Lead FPGA Architects

Getting confused with the technical jargon of FPGA layouts? Don’t fret! Review your RTL roadmaps with our senior engineering team. We provide actionable insights related to MPSoC partitioning, AXI-interconnects, and DO-254 compliance without hefty fees.

Contact form

How can we help you? Leave us your contact details and we will contact you within 24h.

Frequently Asked Questions

What is FPGA design, and why is it used?

FPGA deals with the configuration of Field Programmable Gate Arrays. This approach is used for ultra-low latency, parallel processing, and computing that can be reconfigured. These systems outperform standard CPUs in Edge AI and signal processing.

What is the difference between FPGA RTL design and schematic design?

When it comes to RTL design, the system uses Verilog/VHDL code to define data movement and logic flow. On the other hand, schematic design deals with a physical circuit. It includes power sequencing, high-speed signal routing, and PDN decoupling.

Which hardware description languages do you support?

Our FPGA design company provides complete support for SystemVerilog, VHDL, and traditional Verilog. Also, we use HLS to convert algorithms into hardware.a

What FPGA design flow do you follow?

Our FPGA design tactics follow a rigorous flow:

- Architectural Partitioning

- VHDL or SystemVerilog RTL Coding

- UVM-Based Verification

- Implementation

Can you integrate custom IP cores and high-speed interfaces?

Yes! We can integrate PCIe Gen5/6, DDR4/5 controllers, and Ethernet MACs. Also, we can optimize AXI-interconnects for better data movement.

How do you verify and validate FPGA designs before deployment?

Our team uses UVM for functional testing. As far as the performance is considered, we use STA for validation. Both of these are supplemented by Hardware-in-the-loop (HIL) testing for enhanced validation against physical stressors.

Do you provide FPGA prototyping and hardware validation support?

We support first article prototyping using NA frequency extenders and oscilloscopes. These help validate SerDes signal integrity and power stability without any hassle.

At what stage should a project involve FPGA design expertise?

It is essential to involve us from the initial architectural phase. Our early involvement will ensure optimal hardware-software partitioning and prevent last-stage timing failures. Also, we can help you make an informed decision in the selection of the most cost-effective FPGA or SoC platform.